N.º 46 marzo 1984 275 Ptas.

electrónica: técnica y ocio

#### UN LED PRESUMIDO Y BAILARIN

# CONTRA LOS MISTERIOS PELA ELECTRONICA

P.V.P: 950 Pts. (sin circ. impreso). SUSCRIPTORES: 850 Pts. (sin circ. impr.) Precio del CIRCUITO IMPRESO: 700 Pts.

UN COMIC FASCINANTE, CON INDICACIONES PARA

CONSTRUIR TRES MONTAJES DE INICIACION A LA

ELECTRONICA. EL LIBRO INCLUYE EL RESIMETRO: LA BRUJULA DEL PRINCIPIANTE.

LA ELECTRONICA EN COMICS...

CON MONTAJES PRACTICOS

SI DESEA RECIBIR ESTE LIBRO EN SU DO-MICILIO, UTILICE LA TARJETA DE PEDIDO SITUADA EN LAS PAGINAS CENTRALES DE ESTA REVISTA.

NA RESISTENCIA CHISTOS

publicidad

| SU | N | F | 1 |  |

|----|---|---|---|--|

|    |   |   |   |  |

| <b>Teletipo Elektor</b>                                                                                                                                                      | 3-10 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| <b>Selektor</b>                                                                                                                                                              | 3-13 |

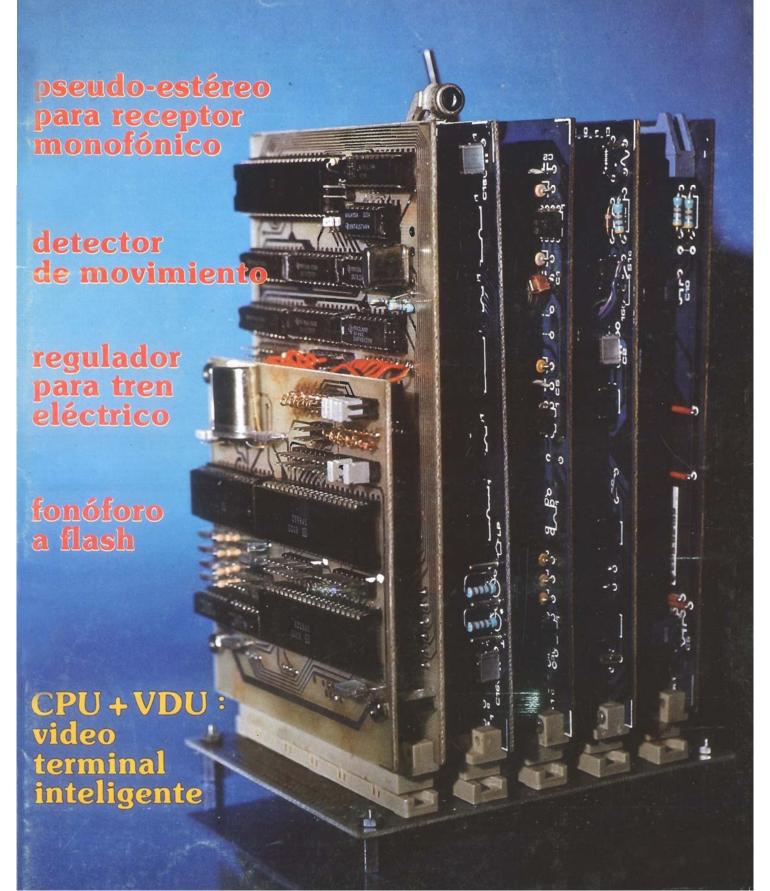

| Tarjeta CPU universal                                                                                                                                                        | 3-15 |

| Regulador para tren eléctrico                                                                                                                                                | 3-23 |

| Barrera de ultrasonidos                                                                                                                                                      | 3-28 |

| <b>Detector de movimiento</b>                                                                                                                                                | 3-31 |

| Interface para calculadora programable                                                                                                                                       | 3-35 |

| Curso de BASIC (17.ª Parte)                                                                                                                                                  | 3-37 |

| Demodulador BLD                                                                                                                                                              | 3-41 |

| Aplikator                                                                                                                                                                    | 3-45 |

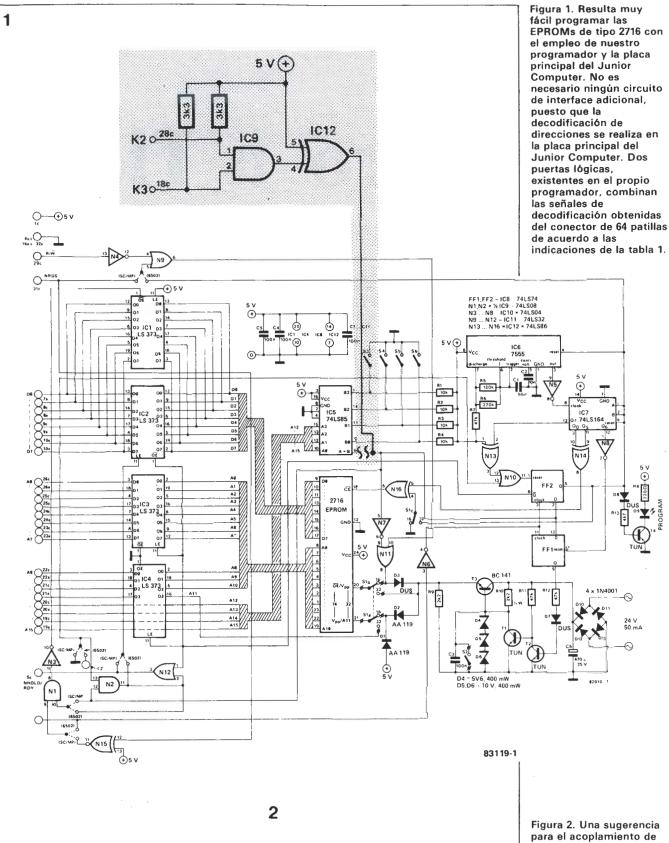

| <b>EPROgramador sin interface</b>                                                                                                                                            | 3-48 |

| Fonóforo a flash                                                                                                                                                             | 3-50 |

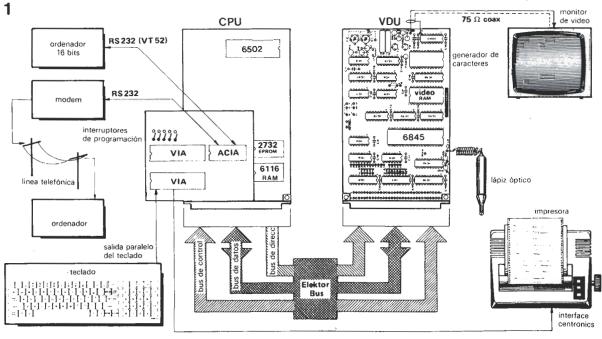

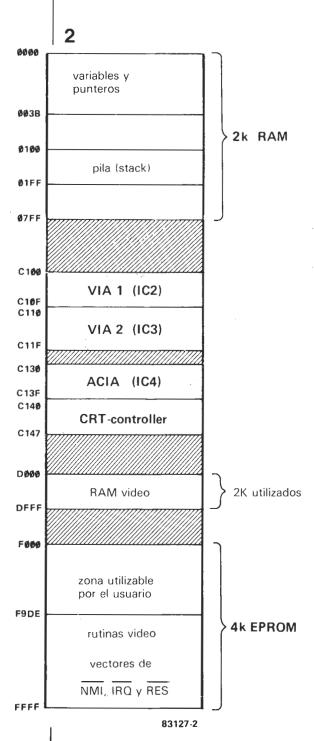

| CPU + VDU = video terminal inteligente El resultado de la combinación de las nuevas tarjetas CPU y VDU, complementadas con el teclado ASCII y una pantalla de visualización. | 3-53 |

| <b>Guía de conexiones para audio</b>                                                                                                                                         | 3-56 |

| <b>Pseudo-estéreo</b> Recepción «pseudo-estereofónica» a partir de la señal monofónica entregada por el Personal-FM.                                                         | 3-60 |

| Mercado                                                                                                                                                                      | 3-64 |

| Indice de anunciantes                                                                                                                                                        | 3-70 |

| Anuncios breves                                                                                                                                                              | 3-72 |

No se trata de la torre de Babel, aunque bien es cierto que puede llegar a manejarse con múltiples lenguajes, sino que se trata de un «nuevo» micro-ordenador al que sólo le falta el cerebro: la tarjeta CPU que presentamos en este mismo número. Las posibilidades que abre la combinación de las nuevas tarjetas para microordenadores con las ya publicadas para el Junior Computer son cuando menos considerables: desde la construcción de un terminal de video universal - descripción que incluimos en este mismo número-, hasta la puesta a punto de un nuevo, moderno y potente microordenador autónomo.

año 5, núm. 46

#### marzo 1984

Redacción, Administración y Suscripciones Edita: Presidente: Director: Redactor iefe edición internacional: Editor adjunto: Redactor jefe de la

edición española Cuerpo de redacción:

Maquetación

Contabilidad:

Distribución:

Impresión:

Suscripciones:

Distribución España:

Distribución Venezuela:

Avda. Alfonso XIII, 141.-bajo, dcha. Madrid-16. Teléf. 250 58 20. Télex: 49371 ELOC E Ingelek, S.A. Ernesto Medina Muñoz Antonio M. Ferrer Abelló Paul Holmes

E. Krempelsauer

Francisco Lara

J. Barendrecht, G. H. K. Dam P. Theunissen, K. Diedrich A. Nachtmann, G. Nachbar, K. S. M. Walraven

Colaboradores: Inmaculada de la Torre, Javier San Juan, Angel Segado, Javier González, Nieves Clemente

Publicidad:

Avda. Alfonso XIII, 141. Teléf. 250 55 79

Madrid-16

Carlos González-Amezúa María Antonia Buitrago Santiago Ferrer María González-Amezúa Gráficas Valencia (Madrid)

COEDIS, Valencia, 245. Barcelona S.A.I. Avda. de los Palos Grandes; Ed. Monte-Ulia 1.er piso, 14, CARACAS. Teléf. 284 78 48 ENEKA, S.A. Avda. Gral Rondeau, 1534. Montevideo. Teléf.: 90 79 44 Distribución Uruguay:

Distribución Argentina: Cía Americana de Ediciones SRL. Sud América, 1532, 1290. Buenos Aires. Teléf.: 21 24 64

ISSN 0211-397X Depósito legal: GU. 3-1980

#### **DERECHOS DE REPRODUCCION**

Elektuur B. V. 6190 AB Beek (L). Holanda.

Elektor Verlag GmbH, 5.133. Gangelt. R.F. de Alemania. Elektor Publishers Ltd. Canterbury CT1 1PE, Kent, Inglaterra.

Elektor Sarl BP 53; 59270 Bailleul, Francia.

Elektor, Via Rosellini, 12. Milano-Italia. Elektor E.P.E. Xanthoulis, Karaiskaki 14, Voula. Atenas-Grecia. Elektor Yayincilik ve Ticaret A.S., Sishane, Estambul. Turquía. Elektor Electronics PVT Ltd., 3 Chunam Lane, Bombay 400007. India.

Elektor Australia Pty Ltd., 11-174 Military Road, Neutral Bay, Sydney. Australia.

#### **DERECHOS DE AUTOR**

La protección de los derechos de autor se extiende no sólo al contenido redaccional de Elektor, sino también a las ilustraciones y circuitos impresos, incluido su diseño, que en ella se reproducen.

Los circuitos y esquemas publicados en Elektor, sólo pueden ser utilizados para fines privados o científicos, pero no comerciales. Su utilización no supone ninguna responsabilidad por parte de la sociedad editora.

La sociedad editora no devolverá los artículos que no haya solicit ado o aceptado para su publicación. Si acepta la publicación de un artículo que le ha sido enviado, tendrá el derecho de modificarlo, traducirlo y utilizarlo para sus otras ediciones y actividades, pagando por ello según la tarifa que tenga en uso. Algunos artículos, dispositivos, componentes, etcétera, descritos en esta revista pue-

den estar patentados. La sociedad no acepta ninguna responsabilidad por no mencionar esta protección o cualquier otra.

#### CORRESPONDENCIA

Para facilitar la labor de administración deberá mencionarse en la esquina superior izquierda del sobre la sigla que corresponda:

Consulta técnica

Suscripciones

DR Director Cambio de dirección CD

SLE Libros y revistas atrasadas Servicio de Software **ESS**

EPS Circuitos impresos Servicio comercial

Publicidad AB Anuncios breves

Copyright © 1984. Uitgeversmaatschappij Elektuur B. V. (Beek, NL) © 1984. Ediciones INGELEK, S.A. (Madrid, E)

Prohibida la reproducción total o parcial, aún citando su procedencia, de los dibujos, fotografías, proyectos y los circuitos impresos, publicados en Elektor.

#### CONTROL DIFUSION

de prenea técnica

¿Qué es un TUN?

¿Qué es un 10 n? ¿Qué es el EPS? ¿Qué es el servicio CT?

¿Qué es el duende de Elektor?

#### Tipos de semiconductores

A menudo, existen un gran número de transistores y diodos con denominaciones diferentes, pero con características similares. Debido a ello, Elektor utiliza, para designarlos, una denominación abre-

- Cuando se indica 741 se entiende que se hace referencia a  $\mu$  A 741, LM 741, MC 641, MIC 741, RM 741, SN 7241, etcė-

- TUP o TUN (Transistor universal de ti-po PNP o NPN, respectivamente) repre-senta a todo transistor de silicio, de baja frecuencia con las siguientes caracteris

| U <sub>CEO.</sub> máx. I <sub>C.</sub> máx. h <sub>EE.</sub> min. Ptot. máx. | 20 V<br>100 mA<br>100<br>100 mW |

|------------------------------------------------------------------------------|---------------------------------|

| f <sub>T.</sub> min.                                                         | 100 mHz                         |

Algunos de los tipos TUN son: las familias BC107, BC108 y BC109; 2N3856A; 2N3859; 2N3860; 2N3904; 2N3947; 2N4124.

Algunos de los tipos TUP son: las fami-lias BC177 y BC178 y el BC179; 2N2412; 2N3251; 2N3906; 2N4126; 2N4291.

· DUS v DUG (Diodo Universal de Sili cio o de Germanio, respectivamente), re-presenta a todo diodo de las siguientes características.

|                       | DUS    | DUG    |

|-----------------------|--------|--------|

| U <sub>R</sub> máx.   | 25 V   | 20 V   |

| I <sub>F</sub> máx.   | 100 mA | 35 mA  |

| I <sub>R</sub> máx.   | 1 A    | 100 A  |

| P <sub>tot</sub> máx. | 250 mW | 250 mW |

| C <sub>D</sub> máx.   | 5 pF   | 10 pF  |

Pertenecen al tipo DUS los siguientes BA127, BA217, BA128, BA221, BA222, BA317, BA318, BAX13, BAY61, IN914, IN4148.

Y pertenecen al tipo DUG: OA85, OA91,

Los tipos BC107B, BC237B, BC547B corresponde a versiones de mayor cali-dad dentro de una misma «familia». En general, pueden ser sustituidos por cual-quier otro miembro de la misma familia.

#### Familias BC107 (-8, -9)

BC107 (-8, -9), BC147 (-8, -9), BC207 (-8, -9), BC347 (-8, -9), BC2317 (-8, -9), BC347 (-8, -9), BC347 (-8, -9), BC347 (-2, -3), BC547 (-8, -9), BC171 (-2, -3), BC182 (-3, -4), BC282 (-3, -4), BC437 (-8, -9), BC414

#### Familias BC177 (-8, -9)

BC177 (-8, -9), BC157 (-8, -9), BC204 (-5, -6), BC307 (-8, -9), BC320 (-1, -2), BC350 (-1, -2), BC557 (-8, -9), BC511 (-2, -3), BC212 (-3, -4), BC512 (-3, -4), BC261 (-2, -3), BC416

#### Valores de resistencias y condensadores

En los valores de las resistencias y de los condensadores se omiten los ceros, siempre que ello es posible. La coma se sustituye por una de las siguientes abreviaturas:

| $= 10^{-12}$       |

|--------------------|

| $= 10^{-9}$        |

| $= 10^{-6}$        |

| — 10 <sup>−3</sup> |

| $= 10^{3}$         |

| $= 10^{6}$         |

| = 10 <sup>9</sup>  |

|                    |

Eiemplos:

Valores de resistencia: 2k7 = 2700 470 = 470

Salvo indicación en contra, las resistencias empleadas en los esquemas son de carbón 1/4 W y 5% de tolerancia máxima

Valores de capacidades 4p7 = 4,7 pF = 0,00000000000047 F 10 = 0,01 μF = 10 <sup>-8</sup>F

El valor de la tensión de los condensadores no electrolíticos se supone, por lo menos, de 60 V; como norma de seguridad conviene que ese valor sea siempre igual o superior al doble de la tensión de

#### Puntos de medida

Salvo indicación en contra, las tensiones indicadas deben medirse con un voltimetro de, al menos, 20 k  $\Omega/V$  de resistencia interna.

Tensiones de corriente alterna Siempre se considera para los diseños, tensión senoidal de 220 V/50 Hz.

#### «U» en vez de «V»

Se emplea el símbolo internacional «U» para indicar tensión, en lugar del símbo-lo ambiguo «V», que se reserva para indicar voltios.

Ejemplo: se emplea  $U_b = 10 \text{ V en vez}$  de  $V_b = 10 \text{ V}$ .

#### Servicios ELEKTOR para los lectores

La mayoría de las realizaciones Elektor van acompañadas de un modelo de circuito impreso. Muchos de ellos se pueden suministrar taladrados y preparados para el montaje. Cada mes Elektor publica la lista de los

circuitos impresos disponibles, bajo la de-nominación EPS (Elektor Print Service).

#### Consultas técnicas:

Cualquier lector puede consultar a la revista cuestiones relacionadas con los circuitos publicados. Las cartas que con-tengan consultas técnicas deben llevar en el sobre las siglas CT e incluir un sobre para la respuesta, franqueado y con la dirección del consultante.'

IMPORTANTE: No se atenderán aque-llas consultas que impliquen una modificación importante o un nuevo diseño.

#### El duende de Elektor:

Toda modificación importante, correc-ción, mejora, etc., de las realizaciones de Elektor se incluirá en este apartado.

#### Cambio de dirección:

Debe advertirse con 6 semanas de antelación.

Tarifa publicitaria (nacional o internacional)

Puede obtenerse mediante petición a la dirección de la revista.

#### LISTA DE PRECIOS

Número sencillo: 275 ptas. Número doble: 500 ptas. Suscripción por un año; España: 2.750 ptas. Europa (correo por superficie): 3.500 ptas. Europa (correo áereo): 3.700 ptas. América (correo superficie): 4.200 ptas. o 28 \$. América (correo aéreo): 6.300 ptas. o 42 \$

Derechos envío certificado: España: 300 ptas. Extranjero: 800 ptas.

#### **OSCILOSCOPIOS**

#### SERIE COS 5000

| G00 5555 | 60 MHz., 3 canales, barrido                               |

|----------|-----------------------------------------------------------|

| CQS-5060 | retardado, linea de retardo                               |

| COS-5041 | 40 MHz, 2 canales, barrido<br>retardado, linea de retardo |

| COS 5040 | 40 MHz, 2 canales<br>linea de retardo                     |

| COS-5021 | 20 MHz., 2 canales<br>barrido retardado                   |

| COS-5020 | 20 MHz, 2 canales                                         |

#### OTROS **MODELOS**

| COS-6100      | 100 MHz., 5 canales, barrido<br>retardado, línea de retardo |

|---------------|-------------------------------------------------------------|

| COS-3010 -TW' | 15 MHz, 2 canales<br>portátii-baterías                      |

| COS-5030-PG   | 35 MHz., 2 canales<br>programable GP-IB                     |

| DSS-6521      | 20 MHz, 2 canales<br>memoria digital GP-iB                  |

| 5516-ST       | memoria de persistencia                                     |

#### CARACTERISTICAS MAS IMPORTANTES

- · T. R. C. plano, rectangular con gratícula interna.

- Alto brillo, aceleración de 12-20 kv.

- Circuito de foco automático.

- Función HOLD-OFF variable.

- Nuevos circuitos con poca deriva y menos consumo,

VIIadomat, 140, bis Tel. 254 4401 / 02 Telex 50.056 TMPL Barcelona - 15

Rda. Segovia, 35 Tel. 265 7414 Madrid - 5

iNUEVO!

Manuales Técnicos Universitarios

Toda la electrónica digital: desde el transistor hasta los circuitos de muy alta escala de integración.

## ELECTRONICA LOGICA MICROPROCESADORES

P.V.P.: 2.300 ptas. Suscriptores: 2.000 ptas.

1.ª Parte

ELECTRONICA

DIGITAL

Algebra de Boole

Puertas-Flip/flops

Contadores-Registros

de desplazamientoMemorias-Conversión

AD/ y D/A

2.ª Parte

MICROPROCESADORES

Teoría de los

Teoría de los microprocesadores y estudio de los más importantes elementos de entrada/salida.

272 páginas

elektor marzo 1984 3-23

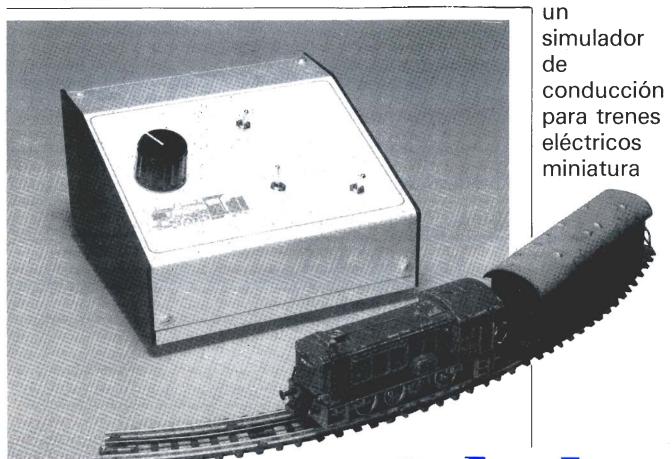

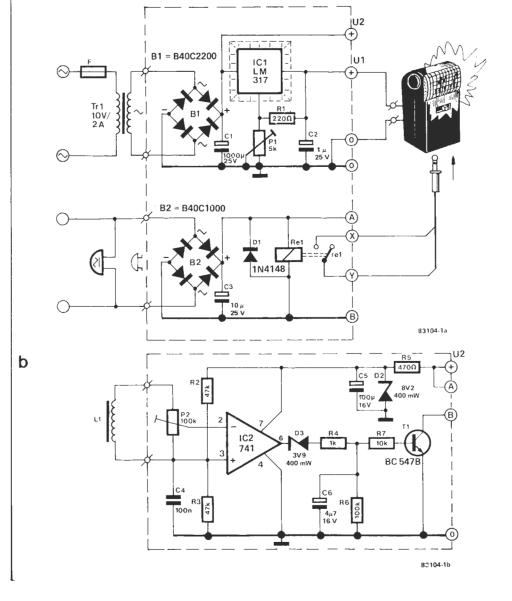

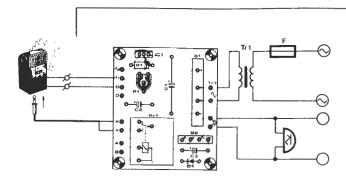

## regulador para tren eléctrico

Los trenes eléctricos son una de las debilidades más compartidas por nuestros lectores. El ejercicio de esta apasionante actividad pasa, casi siempre, por la construcción de una maqueta simulando un paisaje realista. La única nota discordante en esta sinfonía suele ser el comportamiento ferroviario un tanto brusco del propio tren eléctrico. Para que las aceleraciones y deceleraciones de nuestro mimado ingenio sean dignas de los más evolucionados modelos reales, hemos diseñado el regulador para tren eléctrico que describimos en los próximos párrafos.

Nuestro dispositivo podría denominarse de otro modo más ajustado a la realidad de sus prestaciones: «un simulador del comportamiento ferroviario». Veamos de qué es capaz este regulador.

Una simple pulsación del botón de mando y el tren se pondrá en marcha cual si se tratara del expreso de Irún: la aceleración se produce gradualmente, la velocidad crece de forma suave hasta alcanzar la magnitud de la «velocidad de crucero» preestablecida. Si en el curso de esta «toma de velocidad» surgiera un imprevisto no hay por qué preocuparse, puesto que el tren está provisto de un freno de emergencia. También se logra la parada del tren accionando este conmutador y de una forma muy semejante a la real. Y para hacerlo de una manera todavía más real no hay que olvidar la dota-

ción de un «pedal de hombre muerto». Los conductores de trenes miniatura han de tener presente que, en la realidad, los profesionales de los trenes «de verdad» mantienen una presión sobre este pedal a lo largo de todo el recorrido. La interrupción de esta presión sobre el pedal se toma como una indicación de que ocurre algo anormal en la cabina del conductor. En estas condiciones, se accionarán automáticamente los dispositivos de seguridad y se detendrá inmediatamente el tren, con lo que se evitarán posibles catástrofes. En nuestro caso. el pedal en cuestión no se debe mantener continuamente oprimido, sino que sólo hay que accionarlo de forma periódica. Las diversas funciones que acabamos de citar siguen estando a disposición del «conductor» en el caso de que el tren circule marcha atrás

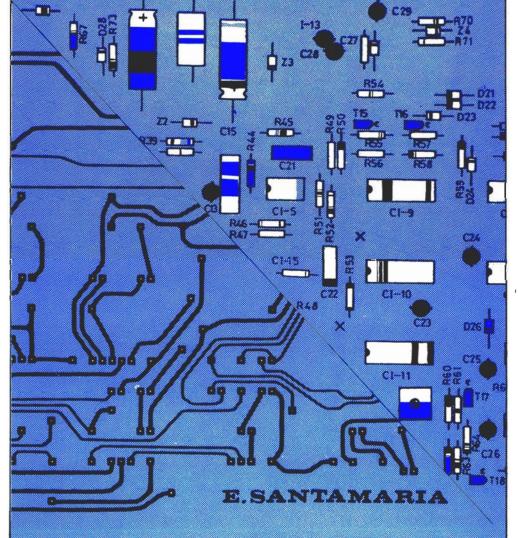

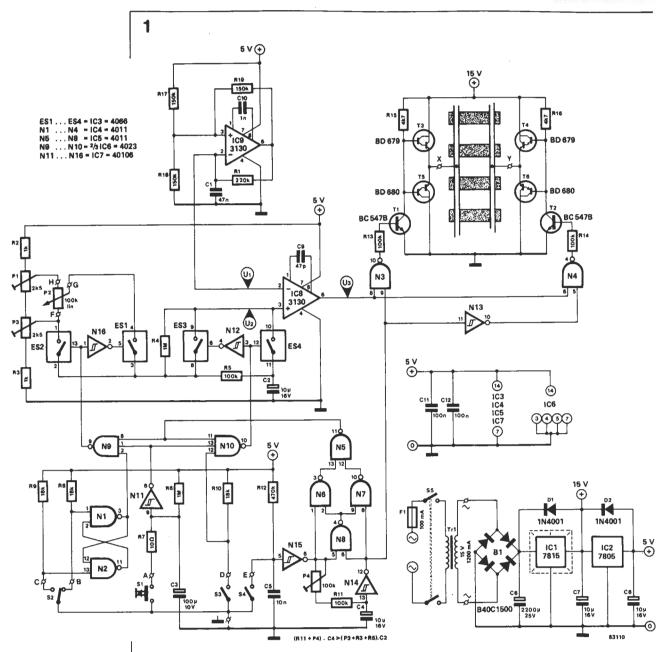

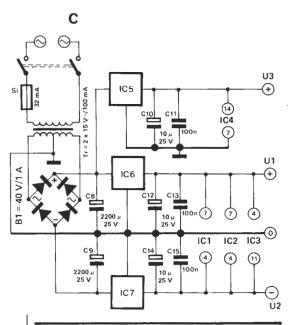

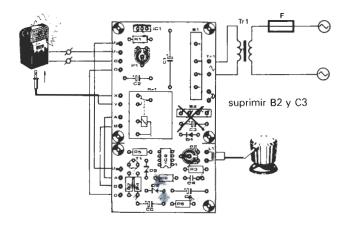

Figura 1. Esquema del circuito regulador para tren eléctrico. El carácter no «exótico» de los componentes permitirá una construcción sin dificultades.

#### El cómo y el por qué

Hay diferencias técnicas que permiten el arranque y la parada con suavidad de un tren eléctrico. Consideremos el caso de una red ferroviaria que funcione con corriente continua. En estas condiciones, basta con «abrir» gradualmente el potenciómetro del transformador de control (como si se tratara de un grifo) para conseguir una salida suave del convoy ferroviario. Si se quiere obtener un resultado idéntico mediante el accionamiento de conmutadores, es preciso dotar al montaje de un dispositivo capaz de hacer aumentar gradualmente la tensión de tracción hasta alcanzar la velocidad de crucero deseada, de manera que se eviten las sacudidas brutales.

Los sistemas que cumplen con los criterios anteriormente indicados son también muy diversos. Después de varias pruebas, hemos optado por el control por modulación en anchura de impulso, en combinación con constantes de tiempo RC. Este sistema se distingue, por una parte, por su gran rendimiento y, por otra parte, por la consecución de un control muy preciso.

Su montaje no exige la adquisición de componentes «exóticos» ni elementos de alto coste, lo que permite conseguir un precio del montaje realmente admisible.

El gran problema que se plantea al diseñar un regulador para tren eléctrico miniatura es la existencia de dos categorías de sistemas: las redes de corriente continua (c.c.) y las redes de corriente alterna (c.a.). No parece posible concebir un regulador universal capaz de funcionar con los dos sistemas. En todo caso, al ser más comunes los sistemas de corriente continua, hemos decidido realizar un montaje adecuado a este caso. Asimismo, para reducir la magnitud del circuito (y por consiguiente, el precio de coste del conjunto) hemos elegido un montaje capaz de controlar un sólo tren a la vez. Cada «circuito ferroviario» ha de estar dotado, pues, de su propio regulador.

#### Gama de posibilidades

El arranque del tren puede activarse de dos formas: «a mano» o accionando un conmutador. En el primer caso, todo sucede como si se tratara de un regulador «ordinario» por medio del posicionamiento gradual de un potenciómetro. Si se elige la versión de conmutadores, se tienen dos opciones: arrancar el tren de forma brusca o ponerlo en marcha suavemente e ir aumentando de forma gradual su velocidad hasta alcanzar el «régimen de crucero». La elección entre estas dos últimas posibilidades se realiza también por medio del basculamiento de un conmutador. El proceso de deceleración hasta la parada completa del tren es idéntico, con las mismas posibilidades de elección entre parada brusca o «civilizada». Para la primera opción basta con tirar de la empuñadura de mando de la señal de alarma (en este caso, accionando el conmutador S2). Lo que equivale a hacerlo más o menos como en la realidad. Por otra parte, si no se ha actuado a tiempo sobre el «pedal de hombre muerto», el tren se detendrá también bruscamente en un momento dado. Es, pues, importante no dejar de vigilar la acción sobre este pedal si no se quiere que el tren se detenga en plena vía sin motivo aparente.

La inversión del sentido de la marcha ocurre de una forma singular: cuando se ha accionado el conmutador correspondiente, el tren comienza por ponerse al «ralentí» hasta detenerse por completo, quedando inmóvil durante unos instantes y volviendo a ponerse en movimiento en el otro sentido (con suavidad, o no, dependiendo de la posición del conmutador S3).

#### El circuito

Los componentes más importantes de la fuente de alimentación son los dos reguladores de tensión integrados conectados «en serie»: el primero (IC1) es un 7815 y el segundo (IC2) es del tipo 7805. El 7815 proporciona la tensión de tracción del tren y no tiene nada que ver con el montaje propiamente dicho. Es el segundo interesado el que suministra la tensión de alimentación para el circuito regulador para tren eléctrico.

Es evidente que IC1 tiene la carga «más pesada» y por consiguiente, debe proveerse de un disipador de calor. Por supuesto, también es necesario que el transformador de alimentación sea capaz de desempeñar esta doble tarea. Es indispensable que cumpla con las especificaciones indicadas. Ambos reguladores están protegidos contra los cortocircuitos y las sobrecargas térmicas importantes.

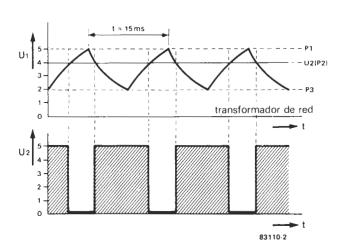

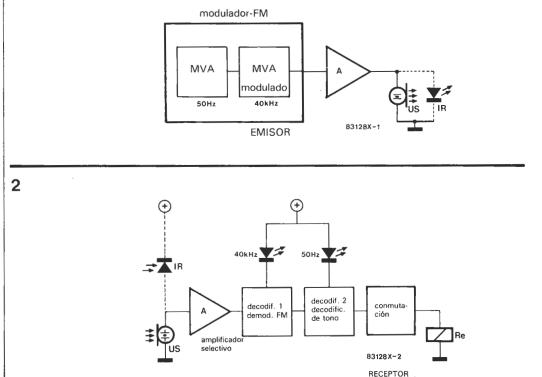

El oscilador basado en IC9 genera la tensión en diente de sierra necesaria para la obtención de un control por anchura de impulso. La señal disponible en la salida del circuito no es, precisamente, la que vamos a utilizar, puesto que se trata de una señal de onda cuadrada que no resulta aprovechable en este caso. Por el contrario, si recurrimos a la señal en diente de sierra (U 1 en la figura 2) presente en la entrada inversora (patilla 2) del oscilador. La tensión en cuestión es, más bien, una pseudotensión en diente de sierra, sin embargo está perfectamente adaptada para el control por anchura de impulso.

El amplificador operacional IC8 montado como comparador realiza la comparación de esta tensión en diente de sierra con la tensión continua existente en el cursor de P2 (U<sub>2</sub> en la figura 2). Dicho potenciómetro permite actuar sobre la anchura de las señales en onda cuadrada de la salida de IC8 (U<sub>3</sub> en la figura 2) y, por consiguiente, sobre la velocidad del tren. Cuando se ha elegido la posición «automática», la posición del cursor de P2 determina la velocidad de crucero del tren. Los límites extremos de esta velocidad se establecen por medio de los potenciómetros ajustables P1 (velocidad máxima) y P3 (velocidad míxima)

El arranque suave automático se consigue de la forma siguiente. Tan pronto como S2 se pone en la posición de puesta en marcha (y en el supuesto de que S3 esté cerrado), el condensador C2 se carga lentamente a través de P2 y de R5. Ello hace que aumente gradualmente la tensión en la entrada no inversora de IC8 a través de ES4. La anchura del impulso de la salida en onda cuadrada de este circuito integrado (U<sub>3</sub>) se hace más grande hasta llegar a alcanzar la anchura máxima, mediante el ajuste de la posición de P2.

#### Lista de componentes:

#### Resistencias:

R1 = 220 k R2,R3 = 1 k R4,R6 = 1 M R5,R11,R13,R14 = 100 k R7 = 10  $\Omega$ R8,R9,R10 = 18 k R12 = 47 k R15,R16 = 4k7 R17,R18,R19 = 150 k P1, P3 = 2k5 ajustable P2 = 100 k lin.

#### Condensadores:

C1 = 47 n cerámico

C2,C4,C7,C8 = 10 µ/16 V

electrolítico

C3 = 100 µ/10 V

electrolítico

C5 = 10 n cerámico

C6 = 2200 µ/25 V

electrolítico

C9 = 47 p cerámico

C10 = 1 n cerámico

C11, C12 = 100 n cerámico

#### Semiconductores:

D1,D2 = 1N4001 IC1 = 7815 IC2 = 7805 IC3 = 4066 IC4,IC5 = 4011 IC6 = 4023 IC7 = 40106 IC8,IC9 = CA 3130 B1 = B 40/C 1500

#### Varios:

S1 = pulsador S2 = conmutador 2 posiciones/1 circuito S3, S4 = interruptor S5 = interruptor bipolar de red Tr1 = transformador de red 15 V/1.2 A F1 = fusible 100mA Radiador para IC1, 35 x 20 x 15 mm, 170°C/W

Figura 2. Fundamento del control por modulación en anchura de impulso (PWM). La anchura de los impulsos y, por consiguiente, la velocidad del tren, dependen del nivel de U 2.

2

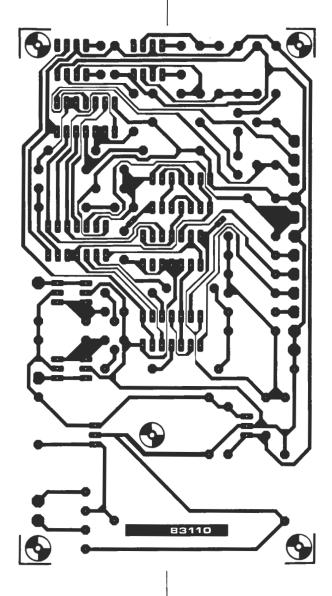

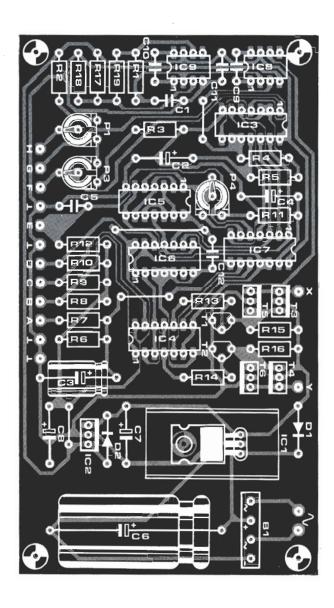

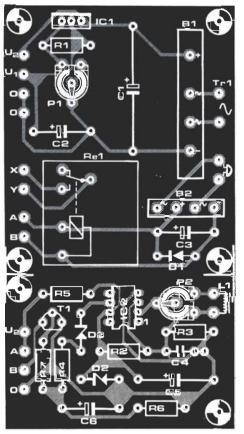

Figura 3. Trazado de las pistas de cobre y serigrafía del circuito impreso diseñado para el montaje del regulador. Los diversos conmutadores pueden colocarse en un pequeño panel de forma que el «conductor del tren» tenga a su alcance todos los elementos de control.

Según el sentido de circulación, estas señales de onda cuadrada excitan a T1 o a T2 que, a su vez, hacen que conduzcan los Darlingtons T3 (T4) ó T5 (T6), respectivamente.

Si, por cualquier motivo, no se quiere arrancar el tren con suavidad, basta abrir el interruptor S3 para hacer que la salida de la puerta N10 adquiera un nivel lógico bajo. Ello hace que ES4 se abra y ES3 se cierre, lo que tiene por efecto «shuntar» la combinación RC y permite al tren arrancar de «golpe y porrazo».

La parada gradual automática del tren se produce de una forma semejante. Hay que poner S2 en la posición de parada y cerrar S3. En esa situación, el biestable constituido por N1 y N2 cambia de estado, de modo que en la patilla 3 de N1 se tenga un nivel lógico bajo y la salida de N9 pasa a nivel alto. Ello hace que ES2 se cierre y ES1 se abra. Entonces, la tensión a través de C2 cae lentamente hasta que se alcanza el valor preestablecido por P3. El resultado de este proceso es, evidentemente, el inverso del que se describió para el arranque: los

pulsos de onda cuadrada se hacen cada vez más estrechos hasta que el tren llega a pararse por completo.

El freno de emergencia incluido en el circuito regulador es una combinación de dos conmutadores: S2 y S3. El freno es accionado al llevar S2 a la posición de parada y cerrar S3 al mismo tiempo. Como en el caso anterior, se shunta de esta forma el dispositivo de temporización y el tren se parará bruscamente. Otra forma de detener el tren es por medio del «pedal de hombre muerto» sin, por supuesto, ninguna acción por su parte. ¿Qué ocurrirá si no se actúa a tiempo sobre dicho pedal? El condensador C3 se cargará lentamente a través de R6 hasta que la tensión en sus bornes alcance la tensión de umbral de la puerta N11, con lo que la salida de esta puerta alcanzará el nivel lógico bajo. En consecuencia, la salida de N9 pasa a nivel alto y se cerrará ES2. Al mismo tiempo, la salida de N16 cae a nivel lógico «0» y se abrirá ES1. La entrada no inversora de IC8 vuelve a estar en su nivel mínimo. Es importante que el tren se detenga inmediatamente tal como sucedería en

la realidad. La parada se produce debido alcambio de nivel en la salida de N11, que también tiene por efecto conmutar la salida de N10 a nivel lógico bajo y «shuntar» el dispositivo de temporización.

Aparte del interruptor doble de red, S5, nos queda por describir la función de S4. Este conmutador sirve para invertir el sentido de la circulación del tren. Por supuesto, no es deseable un cambio brusco del sentido de marcha, sino que el tren debe empezar decelerando hasta la parada completa, punto a partir del que debe entrar de nuevo en movimiento en sentido contrario (brusca o suavemente, según la posición de S3).

Nos interesa, aĥora, saber lo que ocurre cuando se cierra el interruptor S4. Inmediatamente, la salida de N15 pasa a nivel lógico alto. En estas condiciones, la salida (patilla 11) de la puerta OR-exclusiva, basada en N5...N8, pasa a nivel lógico bajo, la salida de N9 adquiere el nivel lógico alto, se cierra ES2 y se abre ES1. En consecuencia, el tren iniciará su deceleración. Al mismo tiempo, el condensador C4 se carga a través de P4 y de R11. Esta temporización es necesaria para dar al tren la posibilidad de detenerse completamente antes de cambiar el sentido de circulación, lo cual sucederá cuando la tensión en los bornes del condensador ha alcanzado un nivel suficiente para llevar la salida de N14 a nivel lógico bajo. No obstante, recordemos que este basculamiento sólo debe ocurrir cuando se haya producido la parada completa del tren. Hay que cuidar que el tiempo invertido en la deceleración sea inferior al tiempo que tarda C4 en cargarse (la duración de la carga depende de la posición de P4).

Cuando la salida de N14 ha pasado a nivel lógico bajo, la salida de la puerta OR-exclusiva (EXOR) y la salida de N3 pasarán a nivel alto. El cambio de estado en la salida de N5 da lugar a que N9 cambie también de estado lógico, por lo que se abrirá ES2 y se cerrará ES1. Al mismo tiempo, la salida de N4 pasará a nivel alto debido a que está a

«1» la salida de N13. El transistor T1 está casi completamente abierto, pero el tren arranca, no obstante, de forma suave, dado que la salida de N4 (y por consiguiente, T2) cambia de estado con la frecuencia de los impulsos de la onda cuadrada, que se hacen progresivamente más anchos. La corriente de tracción se aplica al transistor T5, a través de T4 y del motor de la locomotora. Si se abre el interruptor S4, el proceso es el mismo pero en el orden inverso: la corriente circula desde T3 a T6, a través del motor.

#### Para cada tren, una duración distinta

No resulta de «bello efecto» que un tren rápido moderno se vea «doblado» por una locomotora a vapor de la más antigua generación; ni tampoco lo sería que un tren de mercancías cargado «hasta los topes» acelerara con mayor rapidez que el tren pendular Madrid-París. Con el objeto de conseguir el mayor realismo posible, habrá que tener cuidado para que no se produzcan tales anacronismos. Para ello está, entre otras cosas, nuestro regulador. Con la ayuda de este dispositivo podremos elegir independientemente, para cada convoy, la duración adecuada de la deceleración y el intervalo de tiempo que debe transcurrir entre la puesta en marcha y la obtención de la velocidad de crucero. Los componentes que permiten el ajuste de tal duración son R5 y C2. Este punto se ha dejado a total arbitrio del constructor del montaje, para que proceda a la elección de los valores correspondientes al efecto que quiera lograr. La velocidad de crucero se establece actuando sobre P2. La frecuencia con la que debe accionarse el pedal de hombre muerto (S1) se puede determinar «a satisfacción del consumidor» por medio de los componentes R6 y C3.

En todas partes encontramos barreras de infrarrojos, desde en los circuitos de recuento de objetos hasta en las alarmas domésticas, pasando por los detectores de final de cinta y en los sistemas para la apertura automática de puertas. Por el contrario, los ultrasonidos parecen estar casi «marginados» en estas aplicaciones. A lo largo de este artículo vamos a defender la «causa» de los ultrasonidos, dignos rivales capaces de ofrecer unas prestaciones semejantes a las propias de los infrarrojos.

## barrera de ultrasonidos

## ren rivalidad con los infrarrojos!

Debe haber alguna poderosa razón para que no existan barreras electrónicas de ultrasonidos con rendimientos comparables a los que puede proporcionar una clásica barrera de infrarrojos. La razón es bien sencilla: resulta más fácil obtener una buena inmunidad al ruido en los dispositivos a infrarrojos ¡al fin y al cabo hay más ruido audible que visible! Nuestra tendencia - muy humana, por cierto- al mínimo esfuerzo, ha conducido a que los infrarrojos suplanten a los ultrasonidos en gran número de aplicaciones en las que ambos medios pueden utilizarse con prácticamente las mismas prestaciones. Dicho lo anterior, cabe añadir que no pretendemos «descubrir la pólvora» sino simplemente proponer un circuito ambivalente para ultrasonidos/infrarrojos que funcione adecuadamente en condiciones «normales». Veamos en que se traduce tal proyecto.

#### Fundamentos técnicos

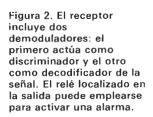

Se sabe que el procedimiento de modulación más seguro es la modulación en frecuencia. También lo hemos utilizado en este circuito confiando en que su fiabilidad nos permitirá obtener el máximo partido de los transductores ultrasónicos. A pesar de ello, el esquema ha quedado bastante simple como se ilustra en las figuras 1 y 2. El emisor está constituido por dos generadores de onda cuadrada y por un amplificador de potencia que controla un transduc-

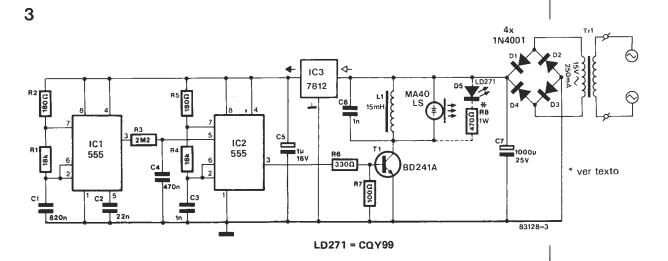

Figura 1. El emisor está constituido básicamente por dos generadores de onda cuadrada que funcionan como un modulador de frecuencia. La señal modulada resultante es objeto de amplificación en una etapa de potencia antes de aplicarla a la barrera.

1

## barrera de ultrasonidos

tor piezoeléctrico o un diodo de infrarrojos. Uno de los generadores oscila a 50 Hz, que es la frecuencia de conmutación. El otro generador proporciona la frecuencia portadora que modulará la señal emitida por el primer generador. El receptor sólo es un poco más complicado. La señal recibida en la entrada, bien sea por la fotocélula de infrarrojos, bien sea por el transductor ultrasónico, se aplica a un amplificador selectivo y luego al discriminador. En este punto, un LED indicará que se ha detectado la portadora. La etapa siguiente es un decodificador de audio, cuya función es detectar la señal útil (frecuencia de conmutación) y lo indica activando un segundo diodo LÉD. El receptor termina en un relé que, si todo va bien según lo previsto, puede disparar un contador, abrir las puertas de un garaje o cualquier otra operación de automatismo dependiendo del sistema con el que se utilice.

#### El circuito

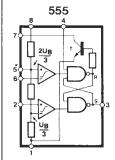

Comencemos por el emisor de la figura 3. Los dos temporizadores 555 constituyen la base de un modulador de FM; por ello están cableados como multivibradores astables (generadores de onda cuadrada). IC1 oscila a una frecuencia de unos 50 Hz e IC2 a unos 40 kHz. Cuando la señal de onda cuadrada de 50 Hz se aplica a la patilla 5 de IC2, las tensiones de umbral de los dos comparadores internos de este circuito integrado están desplazadas en una cierta medida. Cuando el desplazamiento de la tensión se mantiene moderado, se obtendrá una modulación en frecuencia, con una linealidad satisfactoria. Habida cuenta de que numerosos armónicos se generan durante la modulación con tensiones armónicos se generan durante la modulación con tensiones de onda cuadrada, la salida de IC1 (patilla 3) se «redondea» por medio de R3 y de C4.

La salida modulada en frecuencia de IC2 se aplica a la etapa de salida (transistor T1). Este último funciona como un amplificador selectivo que trabaja en la región ultrasónica si se cablea como se indica en la figura 3 (con el circuito oscilante C6/L1 en el circuito de colector). Para el funcionamiento

con infrarrojos, el circuito sintonizado, constituido por el transductor ultrasónico MA40LS, L1 y C6, se sustituye por un diodo emisor LD271 seria con una resistencia limitadora de corriente (R8). Tanto en un caso como en el otro, el circuito de colector está conectado al potencial no estabilizado de la tensión de alimentación. Ello da un desacoplo satisfactorio del modulador y de la etapa de salida. La alimentación del emisor consiste en el clásico terceto «transformador-rectificador-condensador de filtro» (en cuyos bornes se extrae la tensión de colector de T1), al que se unirá el regulador integrado IC3 que estabiliza la tensión de alimentación del modulador. Se constatará que la alimentación del receptor está concedida según el mismo principio (figura 4), con la salvedad de que la tensión es de +5V.

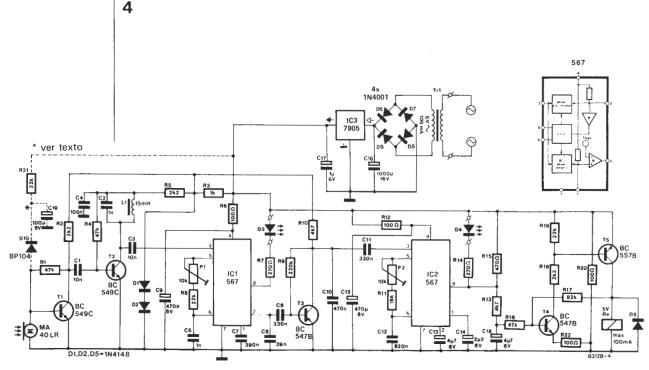

A la entrada del receptor está el transductor US o el diodo IR D10, que se alimenta a través de R21/C18. La señal recibida se amblifica por medio de T1 (cuya ganancia aproximada es de 20). Los diodos D1 y D2, polarizados por R3, aseguran una limitación casi simétrica de la señal en el colector de T1. Además, R3 desacopla la tensión de alimentación para los amplificadores T1, T2 y T3 con respecto a la tensión de alimentación del resto del circuito. Las resistencias R6 y R12 hacen la misma función para los circuitos integrados IC1 e IC2. Estos medios de desacoplo son indispensables para evitar influencias parásitas recíprocas entre las diversas etapas.

La señal amplificada llega al amplificador selectivo T2, cuya configuración es comparable a la existente en el circuito emisor y al que se le pide la extracción de la portadora. En la entrada de IC1, se tendrá, pues, una señal correctamente acondicionada. IC1 contiene un bucle de enganche de fase (PLL) que sirve, en este caso, para la de-modulación de FM. Con la ayuda de P1, R8 y C5, se ajusta la frecuencia central del oscilador interno (IC1) a una frecuencia aproximada de 40 kHz. Asociado a una resistencia integrada, el condensador C6 constituye el filtro de bucle montado entre el detector de fase y el oscilador controlado por tensión (VCO). La señal de FM aplicada en la patilla 3 de IC1 se compara, por medio del detector de fase, con la señal del oscila-

Figura 3. Además de los dos temporizadores del tipo 555, montados como multivibradores astables, el esquema del emisor contiene una alimentación estabilizada cuya tensión rectificada y filtrada, pero no estabilizada, alimenta a la etapa de salida con transductor ultrasónico o diodo para infrarrojos.

dor interno. La señal de error resultante (patilla 2) tiende a corregir la frecuencia del oscilador hasta que sea nulo el desfasaje entre las dos señales comparadas. De este modo, se dispone en la patilla 2 de una señal de 50 Hz, que no es otra cosa más que la moduladora de la señal de FM, aquí obtenida bajo la forma de una señal de error. Esta señal es amplificada por T3 antes de que se aplique al decodificador de audio IC3. En esta ocasión, se ha utilizado el circuito PLL y el desfasador interno (con multiplicador) para detectar la señal de 50 Hz. La señal de salida de IC2 (patilla 8) controla al LED D4, así como a la etapa de conmutación del relé (T4 y T5). En condiciones de reposo, cuando la barrera luminosa o ultrasónica no se vea interrumpida, se encenderá el LED. La base de T4 está a un potencial próximo a masa y este transistor permanece bloqueado lo mismo que T5. Por consiguiente, el relé está desactivado. Cuando el enlace entre el emisor y el receptor (la barrera) se interrumpe por cualquier causa, la salida de IC2 (patilla 8) pasa a un nivel alto próximo al potencial de la alimentación), T4 y T5 conducirán y el relé se activará haciendo sonar un timbre de alarma o un dispositivo similar.

#### Montaje y calibración

El diseño es suficientemente sencillo para permitir que el emisor y el receptor se construyan en una placa pretaladrada de experimentación. No obstante, también es posible utilizar las placas de circuito impreso diseñadas para el semáforo (número de octubre de 1983). Por supuesto, la barrera luminosa y el semáforo no son la misma cosa, pero sus analogías saltan a la vista y no habrán escapado a muchos de nuestros lectores.

Una vez que se haya construido la barrera. habrá que proceder a calibrarla. Por supuesto, es obvio que no se pueden mezclar las dos versiones: el circuito sólo funcionará con ultrasonidos si el emisor y el receptor están provistos de un transductor ultrasónico. Análogamente sucede con la versión para infrarrojos... ¡No se admiten cockteles! Para simplicar aún más las cosas, cabe precisar que el emisor no exige calibración alguna salvo, por supuesto, alinear el «haz» entre el emisor y el receptor. La distancia operativa máxima de un haz de infrarrojos, sin lente, es de unos 6 metros, mientras que con lente es de unos 50 metros. El alcance de un haz ultrasónico sólo puede determinarse por medios experimentales «in situ».

El ajuste empieza colocando los dos potenciómetros ajustables del receptor en la posición media. Cuando no se ha interrumpido la barrera luminosa o ultrasónica, D3 deberá estar encendido; de no ser así, es preciso corregir la posición de P1 para lograr este resultado. En estas condiciones, si D4 sigue sin encenderse ello indica que el haz está cerrado, por lo que habrá que ajustar P2 hasta que se encienda dicho LED. Durante este proceso el relé debe estar en reposo. Una vez conseguida la calibración, se puede suprimir el LED D3 que sirve fundamentalmente para indicar la detección de la portadora en el momento de la calibración. Una advertencia final. Habida cuenta de que la barrera puede utilizarse, sin necesidad de ningún circuito suplementario, como una alarma, hay que tenerse presente que incluso una mosca «bien alimentada» puede interrumpir el haz durante la noche y la consiguiente alarma puede despertar a toda la vecindad. No conviene, pues, un uso abusivo de esta barrera por lo que pudiera afectar a sus cordiales relaciones con el vecindario.

Figura 4. El receptor es bastante más complejo que el emisor. Sin embargo, el empleo de circuitos integrados PLL limita sus dimensiones a lo estrictamente necesario. Según el tipo de barrera deseada (de ultrasonidos o de infrarrojos), la etapa de entrada difiere ligeramente. La etapa de conmutación de salida activa a un relé cuando D4 se apaga; esto es, cuando se interrumpe la barrera.

BP104 = BPW41

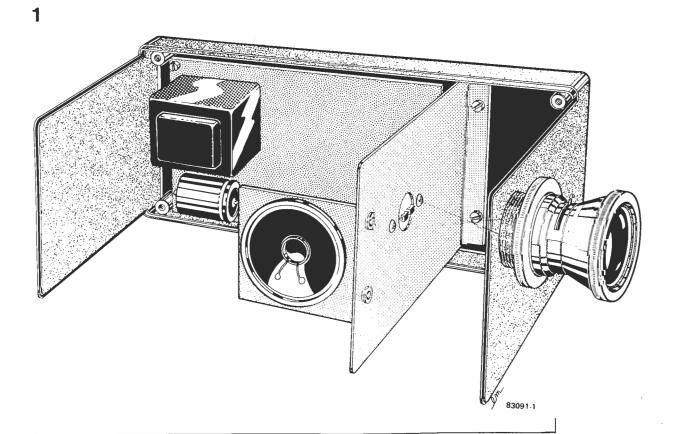

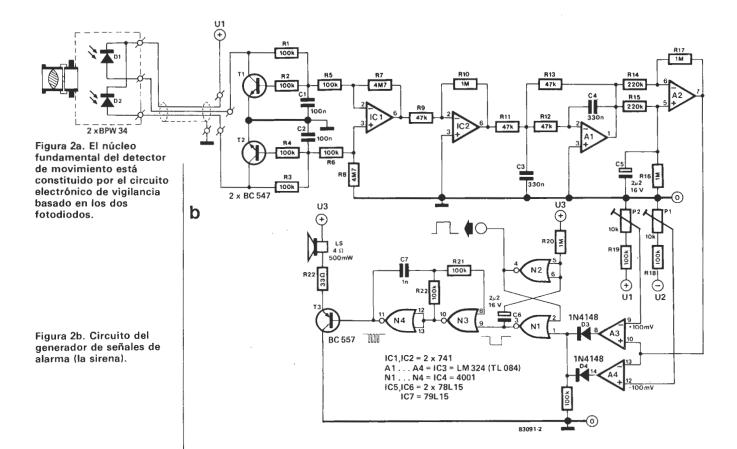

La característica peculiar del detector de movimiento que presentamos es que se trata de un dispositivo pasivo. A diferencia con una barrera luminosa, nuestro vigilante óptico no necesita emisor. El principio fundamental de su funcionamiento es muy similar al del ojo humano.

#### un vigilante óptico

## detector de movimiento

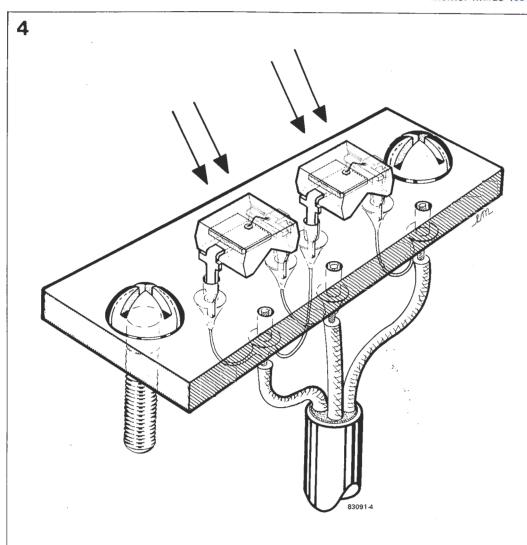

El sensor de este original detector de movimiento está constituida por dos fotodiodos cuya función es muy semejante a la que tienen las células visuales de la retina. Los dos fotodiodos están montados muy próximos entre sí, en el interior de una caja protegida contra la luz. En la ilustración de la figura 1 se observa la forma en la que la que se proyecta una imagen del recinto que se vigila sobre los dos fotodiodos, con la ayuda de una lente óptica. Si la luminosidad ambiente cambia debido, por ejemplo, al paso de nubes, a la llegada del crepúsculo o a cualquier otro fenómeno similar, la variación de la luminosidad es idéntica para los dos fotodiodos. Si, por el contrario, alguna cosa se mueve dentro del campo de visión de la lente (aunque sólo sea un inofensivo canario huido de su jaula), la variación de la luminosidad que incide sobre

los dos diodos es diferente en cada uno de ellos. El circuito es muy sensible a diferencias de muy pequeña magnitud en la intensidad de la luz. Dado su original funcionamiento, es evidente que su principal campo de aplicación será, sin duda alguna, la vigilancia de espacios contra la entrada de intrusos, constituyendo una eficaz alarma antirrobo. Por este motivo, el sistema electrónico del detector está provisto de un módulo generador de señal acústica (algo así como una sirena).

En consecuencia, este montaje podrá sustituir a una barrera luminosa en aquellos casos en los que sea problemático instalar un emisor y un receptor. Por ejemplo, puede utilizarse asociado a una puerta hidráulica para que ésta reciba una orden de apertura en el caso de que se aproxime una persona.

Figura 1. El montaje exige una construcción mecánica robusta y perfectamente hermética a la luz.

#### 2a

Figura 2c. Circuito de la fuente de alimentación con tres reguladores de tensión integrados.

#### El circuito

El esquema del circuito detector se muestra en la figura 2a. Los cátodos de los fotodiodos están alimentados a + 15V y sus ánodos están conectados a un simple filtro activo, que proporciona una (primera) protección contra interferencias. Es recomendable utilizar cable blindado para efectuar la conexión con los fotodiodos y acortar al

máximo la longitud de dichas conexiones. Las bases de T1 y de T2 están desacopladas en alterna por medio de C1 y de C2, respectivamente. Estas dos zonas del montaje son perfectamente idénticas y, por consiguiente, deben eliminar los parásitos producidos por el zumbido de la tensión de red.

Las salidas de c.c. de los filtros se aplican al amplificador diferencial IC1. Mientras no haya movimiento alguno en el espacio vigilado, las tensiones aplicadas a las entradas de IC1 se mantendrán prácticamente constantes e iguales y la salida del amplificador es, pues, muy pequeña. Una variación muy pequeña de la caída de tensión en los bornes de los fotodiodos, a causa de un movimiento en el espacio vigilado, produce una variación rápida e importante de la tensión de salida de este amplificador diferencial. La ganancia de la siguiente etapa, IC2, es del orden de magnitud de 20, por lo que en caso de un fuerte movimiento, la salida de IC2 quedará saturada. La señal de salida de IC2 se hace pasar a través de un filtro suplementario. Se trata de un filtro de paso bajo con una frecuencia de corte inferior a 50 Hz, por lo que impide que cualquier zumbido, u otra señal de muy baja frecuencia, pase a las siguientes etapas amplificadoras constituidas por los amplificadores operacionales A1 y A2.

En este punto del montaje somos capaces

#### detector de movimiento

3

de detectar movimientos en la zona objeto de vigilancia. Como hemos visto, cualquier movimiento da lugar a un rápido incremento del nivel de salida de A1, en tanto que la interferencia se mantenga en un mínimo por medio del filtro. Pero todavía queda un problema sin resolver: en condiciones de reposo, la salida de IC1 tiene ya un nivel de tensión continua determinado y dicho nivel se amplifica a continuación. Por este motivo, no es posible utilizar un simple comparador para obtener una señal de salida sin ambigüedad alguna.

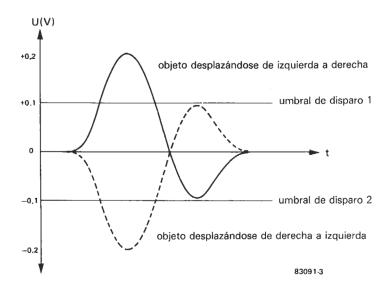

El amplificador operacional A2 se utiliza, pues, como un amplificador diferencial algo modificado. Se trata, en efecto, de un circuito diferenciador controlado, por una parte, por medio de su entrada no inversora, a través de un filtro paso-bajo suplementario de pequeño retardo, construido con la ayuda de C5/R15/R16. De este modo, con un nivel de entrada constante, la salida de A2 estará a 0 voltios. No obstante, un incremento brusco en el nivel de entrada producirá una salida que es similar a la que se muestra en la figura 3.

Los umbrales de conmutación de los circuitos de los comparadores basados en A3 y en A4 pueden ajustarse por medio del accionamiento de los potenciómetros ajustables P1 y P2 respectivamente. A3 y A4 cambian de estado cuando se sobrepasa el umbral positivo o negativo, respectivamente. Las salidas de los dos comparadores se elevan a +15V en uno u otro caso. Los diodos D3 y D4 constituyen una puerta OR para las salidas de los dos circuitos de disparo. En la figura 3 se muestra claramente por qué hemos elegido este diseño que, en principio, puede parecer algo complicado. Después de una señal de iniciación relativamente fuerte, la salida de A2 se amortiguará muy rápidamente. Si el movimiento en el espacio vigilado es relativamente lento y se tiene la consiguiente salida decreciente en A2, es muy posible que nunca se alcance el umbral de disparo positivo. El diseño elegido asegura una mayor sensibilidad y una mejor protección contra la interferencia.

#### Montaje

La construcción de la caja debe realizarse de forma más esmerada que la habitual. Es indispensable que sea perfectamente hermética a la luz (con la excepción de la lente, por supuesto)... de no ser así, podría haberse ahorrado la molestia de construir el sistema electrónico de vigilancia con las más alta sensibilidad. La mejor solución consiste en instalar el montaje directamente en el interior de la propia caja. En la figura 1 sugerimos una posible alternativa para construir una caja a partir de dos chapas de aluminio. El mejor método para asegurarnos de que sea perfectamente hermética a la luz es sellar las pequeñas separaciones entre las chapas con una cinta autoadhesiva ancha y gruesa. La óptica utilizada puede proceder de una vieja cámara fotográfica fuera de uso; por supuesto, no hay que olvidar retirar el obturador (diafragma) o asegurarse de que esté permanentemente abierto. También se puede comprar de segunda mano, si no se dispone de una cámara antigua. Para ello puede recurrir a un catálogo de proveedores de este tipo de artículos.

Los dos fotodiodos están montados muy próximos entre sí en una pequeña placa (o trozo de placa) de experimentación (figura 4). Como se muestra en la figura 1 debe ser posible desplazar la placa dentro de ciertos límites. La distancia entre el objetivo y los fotodiodos hay que determinarla experimentalmente, colocando un trozo de papel blanco lo más cerca posible frente a los diodos y desplazando la placa hasta que aparezca nítidamente la imagen de un objeto situado a la distancia de detección deseada. Una vez conseguido este ajuste, se fijará la placa en su lugar. Como la nitidez de la imagen no es absolutamente indispensable, la placa puede fijarse para distancias «infinitas» como suele hacerse en una cámara fotográfica, dirigiendo el objetivo hacia un fondo paisajístico; de este modo, la distancia efectiva de trabajo se extenderá desde unos 8 metros frente a la lente hasta el infinito.

Figura 3. Representación de la señal de salida del amplificador diferencial. La amplitud de la señal depende de la importancia del movimiento detectado.

detector de movimiento

Figura 4. Los fotodiodos deben montarse cerca uno del otro, soldados en un trozo de placa de experimentación de tipo universal.

#### Verificación práctica

En las pruebas prácticas, el dispositivo reaccionó ante un pequeño movimiento a una distancia de hasta unos 10 metros. También funcionó perfectamente con luz fluorescente, luz diurna o luz crepuscular. Sólo dejó de reaccionar en condiciones de oscuridad absoluta, aunque los fotodiodos se consideran sensibles a la radiación infrarroja. Lamentablemente, la radiación de calor del cuerpo humano cae dentro de una zona del espectro infrarrojo en la que son insensibles los fotodiodos. En la zona de vigilancia podría «iluminarse» con luz infrarroja invisible.

El área de detección del prototipo se extendió únicamente en un ángulo de 30°, no obstante, ello puede mejorarse con el empleo de una lente «gran angular» o utilizando más de un par de diodos, montados en paralelo. Por cada par de diodos debe duplicarse el circuito que termina en la etapa IC1, incluyendo a R9. A continuación, IC2 puede conectarse como un amplificador sumador.

#### Generador de señal de alarma

El esquema de la figura 2b es el de un generador de señal de alarma, aunque puede

considerarse sólo como un ejemplo, puesto que el impulso de salida del detector puede utilizarse para excitar un altavoz de bocina. Las puertas N1 y N2 constituyen un monoestable que tiene por objeto alargar el impulso de activación de entrada, producido por A3 o por A4, hasta una duración de un segundo aproximadamente. Las puertas N3 v N4 forman un multivibrador astable que oscila únicamente cuando el terminal 8 de N3 está a nivel bajo; por consiguiente, su funcionamiento depende de la señal de salida invertida de N1. La salida del astable excita a un altavoz, a través de un amplificador T3. El tono puede modificarse dentro de límites estrechos cambiando el valor de

#### La alimentación

La fuente de alimentación es de tipo convencional con la salvedad de que la alimentación de la zona de la sirena se ha provisto de forma independiente. Esta separación se consideró necesario para evitar cualquier posible realimentación entre las dos etapas del dispositivo, con la consiguiente producción de falsas alarmas. Si el lector tiene la intención de conectar una sirena más potente que disponga de su propia alimentación, puede suprimir la parte de la alimentación situada a partir de IC5 (C10 y C11) en la figura 2c.

### detector de movimiento

Este conversor de fabricación casera hará que se incrementen las posibilidades de su calculadora de bolsillo, proporcionándole una salida binaria de 8 bits que puede conectar, por ejemplo, a un ordenador. Por lo demás, no hay inconveniente alguno en ampliar la salida del circuito de interface a 16 ó 24 bits.

## interface para calculadora

#### Una solución ingeniosa

Las calculadoras de bolsillo programables no suelen disponer de una interface adaptada a las necesidades del usuario. Con nuestra habitual modestia, nos proponemos resolver este problema. Se trata de utilizar dos LDRs (resistencias dependientes de la luz) que se situarán frente a dos dígitos de la visualización de la calculadora. Al encenderse o apagarse los segmentos de estos dígitos visualizados se pueden transmitir con toda facilidad informaciones, en forma de datos binarios, a través de las LDRs a un circuito exterior. En este caso, estas informaciones son datos binarios convertidos por la calculadora TI57 (el programa correspondiente se indica en la tabla 1) a partir de los datos decimales especificados por el programador.

**Funcionamiento**

El funcionamiento de este conversor puede resumirse como se indica a continuación: un dato decimal se convierte en su equivalente binario; los bits correspondientes se transmiten, uno a uno, de acuerdo al apagado o encendido de uno de los displays de 7 segmentos, mientras que otro display contiguo proporciona, con su parpadeo, lo que podríamos denominar una señal de reloj que sirve para sincronizar el circuito de interface. Este visualiza los niveles lógicos de los bits transmitidos a través de LEDs encendidos o apagados.

Aunque este artículo esté orientado al caso específico de la calculadora TI57, también es aplicable a cualquier otra calculadora programable con ligeras modificaciones. En el caso de la TI57, la calculadora proporcionará la señal de reloj en el dígito exponencial y el estado lógico sobre el dígito de la derecha. Para el nivel lógico «1», el display está apagado, mientras que para el nivel lógico «0» se visualizará el carácter « $\pi$ ».

#### El circuito

El esquema del circuito de interface es muy sencillo (ver figura 1). Los niveles lógicos «ópticos», captados por las LDRs, se transforman en niveles lógicos compatibles TTL por medio de los transistores T1 y T2. La señal de reloj es captada por el diodo LDR 1 y es conformada por el monoestable IC1 (74121). La señal de datos es captada por LDR2 y se aplica, sin modificar, a IC2, que es un registro de desplazamiento de 8 bits en paralelo cuya cadencia funcional viene determinada por la señal de reloj anteriormente descrita.

El conmutador pulsador S1 permite llevar la patilla 9 de IC2 a nivel lógico bajo, cuyo efecto será que las ocho salidas, Q<sub>A</sub>...Q<sub>H</sub> se posicionen inmediatamente a nivel «0» (borrado). Cada una de estas salidas suministra al correspondiente LED D1...D8 la corriente suficiente para su encendido (a condición de que, por supuesto, el bit correspondiente está a nivel lógico alto). De no ser así, el LED se mantendrá apagado, con lo que se indica que el nivel lógico

pulso de reloj datos 5 V

P1 100k

BC 547B

BC 547B

BC 547B

BC 547B

P2 11 12 R4

R1 13 R1 13 R1 13 R1 13 R1 14

R1 14 R1 14 R1 14

R1 14 R1 14

R1 14 R1 14

R1 14 R1 14

R1 14 R1 14

R1 14 R1 14

R1 14 R1 14

R1 14 R1 14

R1 14 R1 14

R1 14 R1 14

R1 14 R1 14

R1 14 R1 14

R1 14 R1 14

R1 14 R1 14

R1 14 R1 14

R1 14 R1 14

R1 14 R1 14

R1 14 R1 14

R1 14 R1 14

R1 14 R1 14

R1 14 R1 14

R1 14 R1 14

R1 14 R1 14

R1 14 R1 14

R1 14 R1 14

R1 14 R1 14

R1 14 R1 14

R1 14 R1 14

R1 14 R1 14

R1 14 R1 14

R1 14 R1 14

R1 14 R1 14

R1 14 R1 14

R1 14 R1 14

R1 14 R1 14

R1 14 R1 14

R1 14 R1 14

R1 14 R1 14

R1 14 R1 14

R1 14 R1 14

R1 14 R1 14

R1 14 R1 14

R1 14 R1 14

R1 14 R1 14

R1 14 R1 14

R1 14 R1 14

R1 14 R1 14

R1 14 R1 14

R1 14 R1 14

R1 14 R1 14

R1 14 R1 14

R1 14 R1 14

R1 14 R1 14

R1 14 R1 14

R1 14 R1 14

R1 14 R1 14

R1 14 R1 14

R1 14 R1 14

R1 14 R1 14

R1 14 R1 14

R1 14 R1 14

R1 14 R1 14

R1 14 R1 14

R1 14 R1 14

R1 14 R1 14

R1 14 R1 14

R1 14 R1 14

R1 14 R1 14

R1 14 R1 14

R1 14 R1 14

R1 14 R1 14

R1 14 R1 14

R1 14 R1 14

R1 14 R1 14

R1 14 R1 14

R1 14 R1 14

R1 14 R1 14

R1 14 R1 14

R1 14 R1 14

R1 14 R1 14

conversión decimal/ binario para calculadoras de bolsillo programables

Figura 1. Esquema del circuito de interface para calculadora de bolsillo. El fundamento del circuito consiste en emitir informaciones binarias a partir del encendido o apagados de los displays y tratarlas con la ayuda de un registro de desplazamiento controlado por una señal de reloj que también se transmite a partir del parpadeo de un display.

interface para calculadora Tabla 1. Programa de conversión decimal a binario para la calculadora TI-57.

del bit correspondiente es bajo. En caso de eventuales modificaciones en este circuito de interface, puede ser deseable sustituir los diodos LED por puertas lógicas que dirigirán las palabras binarias hacia otros destinos. Esto no supone inconveniente alguno, con tal de que no se sobrecarguen las salidas de IC2 (que, en teoría, sólo puede suministrar 400  $\,\mu\text{A}$  por cada línea de salida, mientras que cada diodo LED consume unos 15 mA, lo que supone una diferencia notable). En el prototipo se ha utilizado como registro de desplazamiento el circuito integrado 74LS164 de 8 elementos biestables y como monoestable IC1, el integrado 74LS121 por sus buenas características funcionales; no obstante, se pueden utilizar otros circuitos integrados similares.

```

secuencia de introducción

por teclado

Start

ÆΕ

8

STO 4

LRN

STO 1

STO 7

2nd Lbl 1

2nd x > t

GTO 2

2

GTO 1

2nd Lbl 2

2nd x = t

GTO 3

STO 2

GTO 4

2nd Lbl 3

2

STO 2

2nd Lbl 4

2

2nd INV Prd 2

2nd C. t

RCL 1

RCL 2

STO 3

2nd x > t

GTO 5

2nd \pi

2nd Pause

ΕĘ

CLR

GTO 6

2nd Lbl 5

RCL 4

RCL 3

STO 1

2nd Lbl 6

1

x≥t

RCL 2

2nd INV x = t

GTO 4

R/S

RST

LRN

End

```

#### Montaje y ajuste

Todos los componentes del circuito de interface pueden montarse fácilmente en una pequeña placa pretaladrada de tipo universal, a la excepción de las LDRs que deberán instalarse sobre el display de la calculadora. Para esta operación se utilizará cinta adhesiva negra (opaca) que permitirá aislar los LDRs de la luz ambiente. En el caso particular de la calculadora TI57, LDR 1 se montará sobre el display situado más a la izquierda (exponente) y LDR-2 sobre el display correspondiente al primer dígito de la derecha.

Con el programa dado en la tabla 1, los niveles lógicos altos corresponden al apagado de todos los segmentos, mientras que los niveles lógicos altos son traducidos por el signo  $(\pi)$  (pi).

Para el ajuste de la polarización de los transistores y para comprobar el funcionamiento correcto del conversor, se procederá como se indica a continuación:

- Efectuar la conversión decimal a binario de un número relativamente grande (1024, por ejemplo), de manera que el proceso dure el mayor tiempo posible.

- Con la ayuda de un polímetro, medir la tensión en el colector de T1, que debe ser de unos 2 voltios. De no ser así, habrá que ajustar este valor con el potenciómetro P1.

- A continuación, medir la tensión en la patilla 6 de IC1. Dicha tensión debe ser siempre de 0 voltios, con unas pequeñas desviaciones de la aguja en el momento en que se transmiten los impulsos de reloj. Corregir eventualmente la posición de P1 de manera que dicha desviación periódica corresponde a los impulsos de reloj.

- Finalmente, ajustar P2 para obtener una tensión de 2V en el colector de T2. Los diodos LED deben indicar ahora los niveles lógicos del número decimal convertido; por ejemplo, 253 10 = 11111101. De no ser así, reajustar P2 hasta conseguirlo.

Hay que tener en cuenta que con 8 bits, la conversión no puede efectuarse más que para valores decimales comprendidos entre 0 y 255. Quienes deseen una mayor capacidad de conversión podrán ampliar el circuito asociando en serie dos registros de desplazamiento.

#### Observación final

Como se indicó anteriormente, el circuito de interface se presta a otras aplicaciones aparte de la simple conversión decimal a binario. Utilizando los niveles lógicos disponibles en la salida del registro de desplazamiento para controlar otros circuitos (transistores, relés, conmutadores electrónicos, etc.), puede obtenerse un verdadero canal de acceso (port) de salida programable para calculadora de bolsillo. Por medio de puertas suplementarias, sería posible controlar, por ejemplo, la circulación de trenes miniatura. Con un poco de imaginación y de paciencia se puede encontrar otras muchas aplicaciones... ¡Todo es cuestión de experimentar! H

interface para calculadora

#### Simulación Homeostato

Este mes hemos destinado las páginas de nuestro «Curso de BASIC» a un programa fuera de lo corriente; un programa con el que se pretende simular el Homeostato que en su día construyera W. Ross Ashby. La idea de Homeostato está desarrollada en su libro «Desing for a brain» (Proyecto para un cerebro). En sus páginas, W. Ross describe cómo llevo a cabo la construcción de un Homeostato, de acuerdo a la ternología vigente en la época (década de los 50).

¿Qué es un Homeostato? Acudiendo a las raíces griegas del vocablo, «Homeo» es «El mismo, A sí mismo» y «Stato» «Estado» como su propio nombre indica. Uniendo ambos términos podríamos traducir Homeostato por «sistema capaz de permanecer en el mismo estado», o dicho de otro modo: «sistema que logra estabilizarse a sí mismo a fin de conseguir la permanencia en un estado concreto».

De lo dicho hasta el momento cabría pensar que un sistema realimentado es un Homeostato, lo que no es cierto, ya que además de la estabilidad, es preciso que el sistema sea capaz de continuar en su estado aún con fuertes cambios en su entorno e incluso dentro del mismo.

Un ejemplo sencillo de homeostasis, es la piel de nuestro cuerpo, como sistema controlador de la temperatura del organismo. En efecto, de acuerdo a la diferencia de temperatura entre el interior del cuerpo y el medio ambiente y a las necesidades de tomar o expulsar calor, así responderá la piel abriendo y cerrando poros y ensanchando o estrechando los capilares, consiguiendo que la temperatura interna permanezca muy estable.

Por contra, un sistema como es el de los cables que gobiernan el timón de dirección de un avión es estable, pero no homeostático, ya que cualquier ráfaga de viento cambiará el rumbo del avión sin que por otro lado dicho sistema haga nada para corregirlo.

Entramos por tanto en el concepto de ultraestabilidad muy necesario para el desarrollo de sistemas inteligentes.

El Homeostato construido por W. Ross Ashby constaba de varios módulos interconectados entre sí. Cada uno de ellos, estaba unido eléctricamente a uno o varios módulos mediante unos acoplamientos que podían ser fijos o variables. La salida de cada módulo se registraba por medio de un voltímetro de aguja que reflejaba la suma de todas las entradas del bloque. A su vez, ésta tensión se utiliza como entrada de otros bloques, dejando que el conjunto interactuase. Los acoplamientos variables, se conseguían por medio de sendos potenciómetros (control manual) o por medio de uniselectores (control aleatorio). Los uniselectores eran conmutadores rotativos en los que se habían dispuesto las resistencias de modo aleatorio. De este modo, si alguna de las salidas superaba un límite prefijado, mandaba un impulso de avance a los uniselectores localizados en su entrada. De este modo se pretendía conseguir que a través de estos acoplamientos aleatorios el sistema fuese capaz de autoestabilizarse.

Aunque parezca mentira, los sistemas así construidos eran capaces de mantener sus variables esenciales dentro de unos límites y de estabilizarse, a pesar del empeño puesto por los experimentadores en cambiar súbitamente los acoplamientos y desplazar las agujas manualmente.

#### El programa

Por medio de este programa, hemos tratado de simular, utilizando el lenguaje BASIC, los voltímetros, acoplamientos y uniselectores del sistema de W. Ross Ashby. Los voltímetros tienen una cierta inercia mecánica que es simulado mediante una subrutina de integración. El método de integración elegido ha sido el «Runge-Kutta 4.4» por los excelentes resultados que era capaz de ofrecer en comparación con otros métodos de integración. Los topes mecánicos de las agujas, se han creado mediante otra subrutina que limita a un máximo prefijado cualquiera de las salidas del sistema. Para la simulación de los uniselectores se emplea la sentencia RND propia del BASIC. Una posterior transformación consigue situar los coeficientes de acoplamiento entre -- 0,8 y -- 0,2 o entre 0,2 y 0,8. El motivo de ello es evitar un acoplamiento demasiado rigido si el coeficiente es superior a 0,8 o demasiado débil si es inferior a 0,2 en valor absoluto.

Los coeficiente de acoplamiento se han sintetizado en forma de una matriz de dimensión N \* N, siendo N el número de bloques presentes en la simulación. Los «Flags» (indicadores que evidencian si el acoplamiento puede o no variar aleatoriamente) se encuentran, así mismo, en forma de matriz. La referencia a un acoplamiento concreto es:K (salida — entrada). Por ejemplo K (1,3) es el coeficiente de la salida del bloque 1 que entra al bloque 3. Y la referencia de un Flag F (1,3) =: 1 nos indica que el acoplamiento puede variar aleatoriamente.

También se han previsto entradas manuales en cada uno de los bloques con el fin de poder crear estímulos externos.

En la primera de las simulaciones, se ha pretendido representar un experimento ya realizado en laboratorios. Consiste en una operación quirúrgica en la que se permutaba los nervios excitadores de los músculos tensores y extensores del brazo de un mono. Después de la operación, el vituperado animal tuvo serios problemas a la hora de poder coger su alimento. Si la comida se encontraba a la derecha su brazo se dirigía hacia la izquierda. Esta situación no fue permanente, pues el cerebro del animal comenzó a establecer las nuevas relaciones entre lo que él quería y lo que su brazo ejecutaba y tras un período de reaprendizaje consiguió controlar de nuevo su brazo.

Nosotros hemos tomado un bloque como cerebro,

0:

otro como músculos tensores (D) y otro como músculos extensores (I). El acoplamiento entre cerebro y músculos es fijo y el de respuesta conseguida por los músculos hacia el cerebro es variable aleatoriamente. Al empezar el programa, un impulso positivo del cerebro encontraba como respuesta un impulso positivo de tensores y negativo de extensores... y viceversa. En un momento determinado se permutaron los acoplamientos entre cerebro y músculos. Al mandar una nueva orden, el conjunto se vuelve inestable dando lugar a la actuación de los uniselectores, los cuales fijaron aleatoriamente unos nuevos coeficientes entre respuesta de músculos y cerebro.

En la simulación que presentamos se ha conseguido llegar a un estado establa al primer cambio. Aplicando de nuevo un impulso desde el cerebro, observamos que la reacción obtenida es contraria a la registrada antes de la operación o, dicho de otro modo, el sistema ha aprendido de nuevo.

En la segunda de las simulaciones nos hemos arriesgado a domar un león salvaje. Uno de los bloques hace las veces de látigo del domador (D), otro de león (L) y un tercer bloque auxiliar (A) se ocupa de enlazar la respuesta del león hacia el látigo.

Pretendemos conseguir que ante un impulso positivo del domador el león nos responda con un impulso negativo y viceversa. Caso de no ser así se puede aplicar un castigo consistente en desplazar la variable esencial del león (L) fuera de los límites. Al ejecutar el programa, un pequeño impulso del domador desequilibra todo el sistema. La actuación de los uniselectores fija unos nuevos acoplamientos que logran estabilizar todo el conjunto. Un impulso positivo del domador tiene ahora por respuesta un impulso también positivo del león, por lo que se le aplica un castigo. Los uniselectores tienen que actuar ahora por dos veces consecutivas para lograr una nueva estabilidad. Con estos parámetros, realizamos una nueva prueba. La respuesta del león ante un impulso positivo es ahora negativa y viceversa, lo cual era, ni más ni menos, el objetivo pretendido en la doma. De no haberlo conseguido - ¡pobre león! - se hubiesen seguido aplicando castigos hasta lograr el comportamiento deseado.

#### Variables y constantes del programa

Las variables empleadas en ambas simulaciones son idénticas en su función, tomando valores distintos en cada caso para conseguir una u otra estructura.

N: Número de bloques que intervienen.

K: Matriz de acoplamientos entre bloques.

F: Matriz de Flags que permiten el cambio aleatorio.

C\$: Matriz de símbolos que represen-

tan cada bloque. Matriz de los valores de salida de

los bloques.

01: Matriz auxiliar para el cálculo de las

Coeficientes de realimentación inl: terna de cada bloque para propia

estabilidad.

E: Matriz de excitación externa de los

bloques.

IN\$: Auxiliar para respuestas de un sólo

carácter.

T: Incremento de tiempo para inte-

gración.

TI: Número de incrementos de tiempo

para presentación de nuevos valo-

res de salida.

TU: Número de ciclos de presentación

para nueva actuación de los unise-

lectores.

TP: Tiempo transcurrido desde el co-

mienzo.

OM: Máximo valor absoluto de cual-

quier salida.

VE: Umbral de disparo para actuación

de uniselectores.

LW: Ancho de línea.

Matriz auxiliar para tabulación de TB:

las salidas.

T1, T2, I: Variables de indexación en los

bucles.

Auxiliares para la integración. K1, K2, K3, K4:

PS:

Posición de salida en representación gráfica.

Los bloques del programa son similares al igual que las variables. Podemos descomponer el programa en:

10-80: Presentación del programa.

Matrices de variables y coeficientes. 100-120: 200-290: Instrucciones de actuación externa. Bloque de especificación de acopla-300-399:

mientos.

Coeficientes y parámetros de simula-400-590:

ción.

600-650: Cálculo de parámetros de visualiza-

ción.

1000-9999: Bloque repetitivo de procesado.

1100-1400: Toma de órdenes desde teclado.

Los anteriores bloques se deben adaptar de acuerdo a las necesidades impuestas en cada caso.

Los siguientes bloques no precisan de cambio alguno puesto que se han desarrollado como subrutinas independientes.

10000-10290: Integración Runge-Kutta 4,4.

Limitación del valor de las salidas. 10300-10900:

11000-11900: Visualización de los datos. Actuación de los uniselectores. 12000-12900:

¡A simular!

##

```

10360 NEXT I

10900 RETURN

11000 REM SUBRUTINA DE VISUALIZACION

11010 FOR 1=1 TO N

11020 PS=D(1)=K

11030 IF PS < -LV THEN PS=-LV

11030 IF PS > -LV THEN PS=-LV

11040 IF PS > LV THEN PS=LV

11050 IF INT(PS)>O THEN PRINT TAB(TB(I)) "!";

11060 PRINT TAB(PS+TB(I)) C5 (I);

11070 IF INT(PS)<O THEN PRINT TAB(TB(I)) "'";

11090 NEXT I

11090 RETURN

11990 RETURN

12000 REM POSIBILIDAD DE UNISELECTORES

11900 RETURN

12000 REM POSIBILIDAD DE UNISELECTORES

12005 PRINT "UNISEL-->";

12010 FOR 1=1 TO N

12020 FOR 0=1 TO N

12030 IF F(0,1) = 0 GOTU 12200

12100 IF ABS(O(1)) < VE GOTO 12200

12105 PRINT

12110 K(0,1)=(RND(1)*.6*.2)*SGN(RND(1)=.5)

12120 PRINT "K"; 0; ","; I : "~"; INT(k(0,1)*100)/100

12200 NEXT 0

12210 NEXT 1

12990 RETURN

```

## \_\_BASIC\_\_ (17 PARTE)

```

LIST

520 TI=5 : REM TIEMPO PRESENTACION NUEVOS DATOS

530 TP=0

540 TU=20 : REM CICLOS PARA ACTUACION UNISELECTORES

580 OH=30

590 VE=OH=-5

600 REM PARAMETROS DE VISUALIZACION

610 K=1/N ; LM=60

620 LV=LM=WK/2-1

630 FOR I=1 TO N

640 TB(I)=10+LM=K*(I-5)

650 NEXT I

1000 REM PROCESO DE SIMULACION

1010 FOR T1=1 TO TI

1030 GSUB 10000 : REM INTEGRACION

1010 FOR T2=1 TO TI

1030 GSUB 10000 : REM INTEGRACION

1040 TP=TP+T

1050 NEXT T2

1060 GSUB 11000 : REM VISUALIZACION

1070 GET INN : IF INN=-"" GOTO 1200

1100 FOR ORDENES DESDE TECLADO

1110 FOR I=1 TO N

1120 IF INN<->"C" GOTO 1400

1120 FOR INS-C" GOTO 1400

1210 REM CASTIGO AL NO RESPONDER CORRECTAMENTE

1220 E(2)=100 : REM CASTIGO EN FORMA DE SOBREIMPULSO

1230 OFINIT "CASTIGO" : PRINT "-----"

1410 GSUB 12000 : REM ACTUACION UNISELECTORES

1500 GOTO 1000

9999 END

10000 REM INTEGRACION RUNGE-KUTTA

10010 FOR I=1 TO N

10040 E==(1) : REM EXCITACION EXTERNA DE LA UNIDAD

10025 E(1)=E(1)=SGR(E(1))

10035 NEXT S

10100 KI=1(1)=0(1)+E

1010 (X=1(1))=(0(1)+S)+E

10100 (X=1(1)=

```

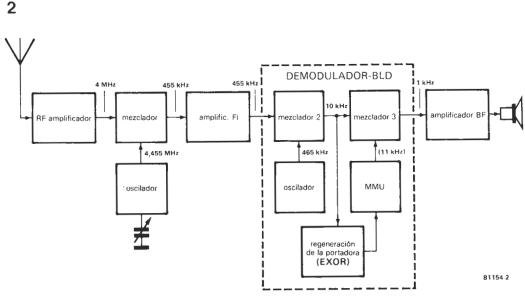

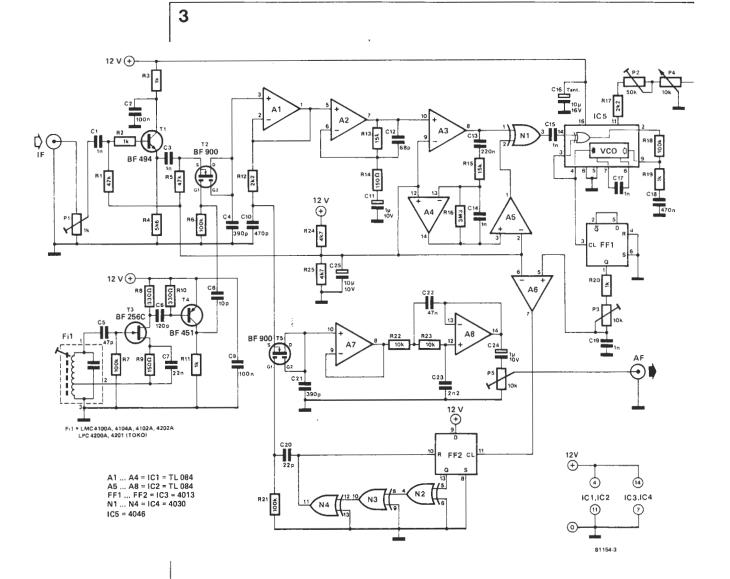

En un artículo anterior tratamos de los principios teóricos de un receptor de BLU, artículo que complementamos con la realización práctica de un receptor de este tipo. Ahora pretendemos introducir al lector en otra clase de modulación que denominamos de portadora suprimida y banda lateral doble (DSB-SC, para los ingleses), y que abreviaremos con las siglas BLD. Nos concentraremos en el demodulador de BLD, de concepción tecnológica revolucionaria, dirigido a quienes desean profundizar en esta nueva técnica.

## demodulador BLD

La modulación de amplitud tradicional (AM) con portadora debe ser ya bastante familiar a nuestros lectores. A nivel mundial, se emiten y se reciben ondas de todas las longitudes: cortas, medias y largas. De hecho, parece ser que el descubrimiento de la técnica de detección ha resuelto todos los problemas que pudiera plantear esta clase de modulación. No obstante, por muy diversas e importantes razones, el campo de las telecomunicaciones ha proporcionado estímulos para «inventar» muchos otros métodos de modulación analógicos y digitales; ellos están, sin duda, plenamente justificados, no obstante, las exigencias impuestas al receptor son diametralmente opuestas cuando se pasa de una forma a otra de modulación.

#### Un poco de teoría

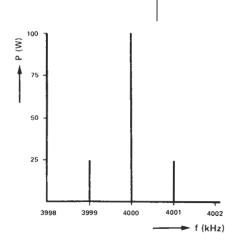

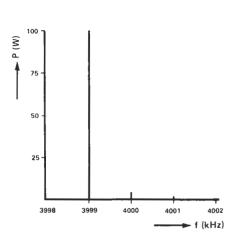

Es muy difícil exponer las razones del éxito limitado encontrado por la BLD. Algunas malas lenguas pretenden que los intereses creados en la BLU hicieron valer su influencia en el momento decisivo. Es posible que la técnica de la BLU estuviera mejor desarrollada, en su momento, que la técnica de la BLD. En cualquier caso, con respecto al empleo eficaz de la potencia del transmisor, la técnica de BLD representa un punto a medio camino entre la modulación en amplitud (AM) y la modulación de banda lateral única (BLU), como se ilustra en la figura 1. Si, por ejemplo, una portadora sinusoidal de una frecuencia de 4 MHz se modula con una «señal de información» sinusoidal, de una frecuencia de 1 kHz, se producen dos «frecuencias laterales», además de la frecuencia portadora (3.999 kHz y 4.001 kHz).

Por supuesto, no nos vamos a sumergir en una serie de fórmulas matemáticas, unas más complejas que otras, para intentar poner de manifiesto el fundamento teórico de la formación de dichas dos bandas laterales

Nos llevaría demasiado tiempo y espacio y queda evidentemente fuera del objetivo que hemos concebido para el presente artículo.

En la figura 1 se muestra una señal modulada tal como se visualiza en un analizador de espectro. La diferencia entre un osciloscopio que da la potencia de una señal en función de su duración y un analizador de espectro es que este último proporciona la potencia de una señal en función de su frecuencia. Los diversos componentes de una señal son, así, analizados en función de su frecuencia. En el supuesto de que la señal de información no esté constituida por una sola frecuencia sino por una mezcla de frecuencias, se obtienen bandas, en lugar de líneas, en el espectro de la señal modulada, una a la izquierda y otra a la derecha de la portadora. Ambas bandas contienen precisamente la misma información. La portadora no contiene ninguna información pero requiere la mayor parte de la potencia, como puede constatarse en la figura 1. Por consiguiente, si se suprime la portadora durante la transmisión y la energía que contiene se transmite a las bandas laterales transportadoras de información, se obtiene como resultado las dos clases de modulación de BLD y BLU. Ya hemos tratado en otros artículos las ventajas e inconvenientes de la banda lateral única (BLU) y ahora, vamos a ocuparnos de la BLD. Con la banda lateral doble, sin embargo, la portadora debe regenerarse en el extremo receptor, lo que constituye una dura prueba por lo que respecta a la estabilidad de frecuencia del modulador.